超越摩尔时代的集成新路径与新技术

摘要

随着集成电路技术逼近摩尔定律(Moore's law)的物理极限,传统芯片制程面临材料、器件及架构瓶颈.基于国家自然科学基金委员会第393期双清论坛本文总结了超越摩尔时代半导体集成中的新材料、新器件和新架构的研究进展与未来发展方向,凝练了未来5∼10年亟待解决的关键科学问题和技术挑战,包括碳基材料、(超)宽禁带半导体材料、二维材料等新材料;集成自旋量子比特、宽禁带半导体功率器件、宽禁带半导体射频器件等微电子器件;硅基光电子器件、微型发光二极管等光电子器件;光电异质融合集成、存算一体芯片架构等体系新架构. 同时,提出了“多域多场异质集成技术"发展路径, 以支撑超越摩尔时代的产业变革,并制定技术路线图及政策建议, 旨在推动我国集成电路技术持续创新和突破.

关键词 #超越摩尔定律, #集成电路, #新材料/新器件/新架构, #光电异质融合, #异构集成技术

1 超越摩尔时代半导体集成的研究现状与发展趋势

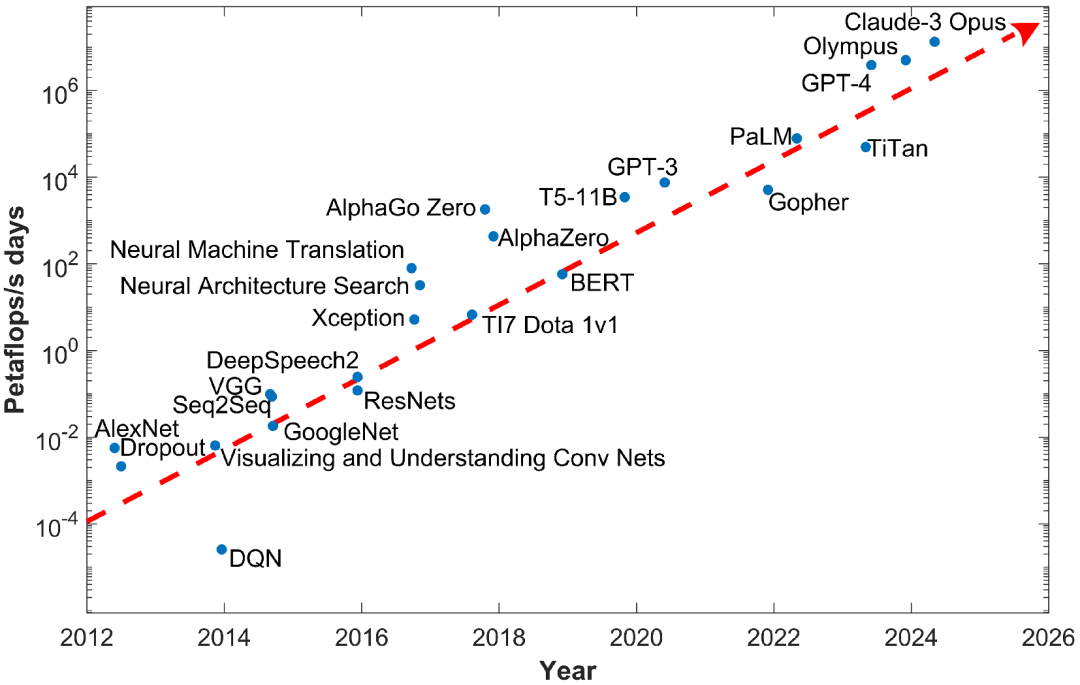

当前全球科技竞争日益激烈, 集成电路技术正处于竞争的最前沿. 集成电路是现代信息技术的基石, 是国家经济建设、社会发展、国防安全的重要基础, 是国家科技自立自强的核心支撑点. 半个多世纪以来, 集成电路的发展主要依靠尺寸微缩技术, 即摩尔定律, 实现性能的指数提升, 但随着工艺进入5 nm时代, 尺寸微缩已经接近物理极限. “超越摩尔时代”成为半导体发展的一个新阶段, 超越是一个长期过程, 在已有的成果基础上不断探索寻找新路径、新技术, 从而获得新的突破. 随着大数据时代的到来, 各行业对算力的需求爆发式增长, 如图1所示. 传统的依赖于单一处理器算力性能提升的方式已无法满足这些日益增长的需求. 半导体材料、器件、架构及其集成技术是最核心的底层技术. 在超越摩尔时代的进程中, 通过半导体新材料、新器件和新架构的协同创新, 才能在更高效、更低功耗的前提下全面提升系统各类性能, 突破现有技术瓶颈, 推动大数据时代的科技发展.

图1 算力的需求增长曲线

首先, 整体架构层面的全新设计和深度优化对数据传输能力的提升至关重要. 随着5G, 6G等新一代通信技术的推广和普及, 数据传输速度成为整体系统能否满足算力提升需求的瓶颈. 新一代计算系统架构不仅需要综合考虑不同功能模块之间的协同效应, 还要合理规划各类器件的布局与集成, 确保计算、存储、电源管理和数据传输的需求得到平衡. 光电异质融合集成技术能够突破传统电路的带宽限制, 提供更高效、稳定的数据传输通道. 光电异质集成技术通过光与电的结合, 使得不同类型的器件(如光电子、射频电子等)能够在同一芯片上高效协同工作, 能在数据传输和处理过程中提供更高效的计算和传输能力, 极大提升系统集成度.

其次, 如何运用新材料实现高性能的存储器、数据传输器件、电源管理器同样尤为重要. 其中, 高效能存储技术的需求尤为迫切. 这些新型存储器不仅需要更高的存储密度, 还应能够实现更快速的读写操作, 以支撑海量数据的实时处理和快速访问. 对于大规模数据分析和人工智能训练等高强度计算任务, 传统存储计算分离架构成为了性能瓶颈. 新型材料实现存算一体技术不仅能提升存储密度, 还能提高数据流动效率, 减少数据存取延迟, 从而提升整体性能. 随着算力的增加, 功耗问题日益严重, 高效的电源管理是计算系统效率提升的关键因素之一. 尤其在数据中心和云计算平台等场景中, 高效电源管理技术尤为重要. 宽禁带半导体功率电子器件和低功耗设计能够有效降低能耗并延长硬件的寿命.

此外, 通过新型器件的异质集成新技术实现更高效、更紧凑的极大规模极限微缩系统也非常重要. 超越摩尔定律的进程还致力于在极小空间内集成传感器、射频器件、功率器件和处理器等多种功能, 通过系统级优化提高整体性能. 新型信息器件的异质集成技术为实现更高效、更紧凑的计算和通信系统提供了新的可能性.

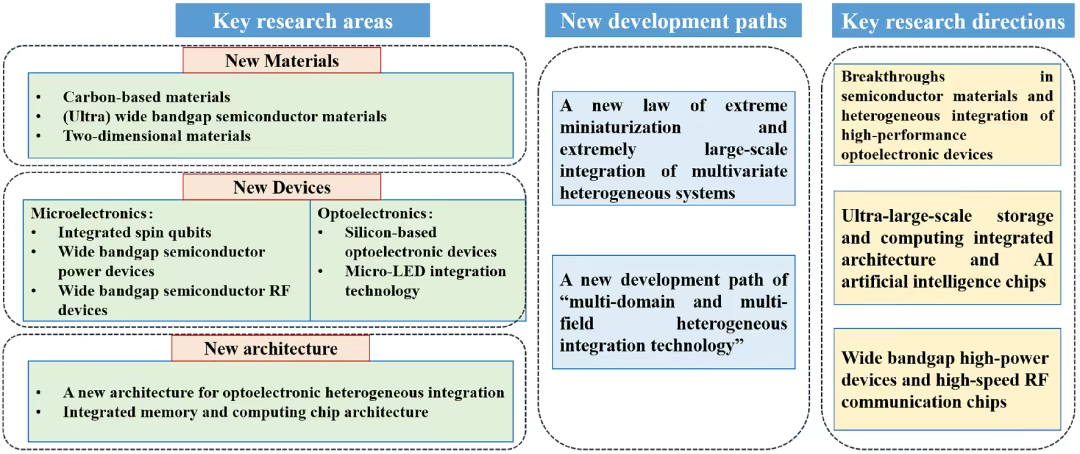

本文从超越摩尔时代的半导体新材料–新器件–新架构多层次分析了超越摩尔时代的集成新路径与新技术领域, 如图2所示. 同时, 提出了多元异质体系极限微缩与极大规模集成规律是超越摩尔时代的关键, 并提出了“多域多场异质集成技术”的新发展路径. 该技术旨在通过多领域、多物理场的协同创新, 将不同材料、不同功能、不同工艺的器件集成在同一芯片或系统中, 突破传统集成电路在材料、器件和架构上的瓶颈, 推动开展高性能、新功能、新机制、新应用为牵引的新材料/新器件/新架构融合研究, 以支撑超越摩尔时代半导体领域的持续发展, 为半导体集成新路径与新技术中国发展路线图绘制奠定了基础.

图2 基于半导体新材料/新器件/新架构的超越摩尔时代的集成新路径与新技术领域

具体研究现状与发展趋势分析如下.

1.1 超越摩尔时代的半导体新材料

传统硅技术的持续缩小面临诸多挑战, 尤其是在功耗、热管理、性能和集成度方面. 因此, 探索和开发新型半导体材料, 尤其是能够超越硅材料的物理限制的材料, 成为了当前科技领域的热点.

1.1.1 碳基材料

碳基材料的研发不仅是半导体行业的突破口, 更在多个高新技术领域逐渐展现出应用潜力. 而碳基材料以其优异的电子、机械和热性能, 提供了新的解决方案. 例如碳纳米管(carbon nanotubes, CNTs)具有极强的机械强度和出色的导电性,

尤其是单壁碳纳米管(single-walled carbon nanotubes, SWCNTs)的导电性能远远优于铜等传统导体. 2021年 Nature Electronics 报道了碳纳米管阵列射频晶体管[1].

2022年 Science 报道了基于碳纳米管的晶体管[2]. 2024年 Nature Electronics 报道了基于碳纳米管的张量处理器芯片[3]. 在日本, NEC和富士通(Fujitsu)等公司利用碳纳米管研发了下一代电子元件, 如透明导电膜和高效储能电池. NEC曾展示过一个碳纳米管晶体管, 工作频率高达500 GHz, 这为未来超高速通信设备奠定了基础. 此外, 碳纳米管在能源存储领域也获得了广泛关注. 美国麻省理工学院(Massachusetts Institute of Technology, MIT)的研究人员成功利用碳纳米管制造出了一种高性能超级电容器, 能够在短时间内存储并释放能量, 未来有望应用于电动汽车和可再生能源领域[4].

当前, 碳基材料的研发正处于从实验室到产业化应用的过渡阶段. 石墨烯和碳纳米管在电子、光电、储能等领域展示了巨大的应用潜力, 然而, 其大规模商业化仍面临着制备工艺复杂、成本高昂等问题. 未来的研究将更加聚焦于如何提升碳基材料的制备效率与一致性, 以及探索其与现有硅基工艺的整合, 以推动其在半导体、传感器、能源存储和生物医疗等多个领域的广泛应用. 例如, 全球多家研究机构正在探索石墨烯与硅基器件的混合制造, 试图借助石墨烯的高迁移率特性提高传统晶体管的性能. 此外, 碳基材料在量子计算、人工智能、5G/6G通信以及脑机接口等前沿技术中也有望发挥重要作用, 成为推动超越摩尔定律时代技术变革的重要力量.

1.1.2 (超)宽禁带半导体材料

随着传统硅基半导体技术接近其物理极限, 宽禁带(wide bandgap, WBG)和超宽禁带(ultra-wide bandgap, UWBG)半导体材料正在成为新一代电子器件和系统的核心推动力. 这些新材料具有更宽的禁带宽度, 超越了硅的限制, 能够在高压、高温、高频和强辐射等极端条件下工作, 从而在电力电子、光电器件和通信领域展现出广泛应用前景. 它们的引入和发展被视为应对“后摩尔时代”挑战的关键路径, 为半导体行业突破摩尔定律的束缚提供了全新方向.

当前, 宽禁带材料,如碳化硅(SiC)和氮化镓(GaN), 已经在高效功率转换领域取得了显著进展. 碳化硅器件凭借其更高的热导率、更低的功率损耗和更强的抗电压能力, 广泛应用于电动汽车、智能电网和可再生能源系统中, 有效提升了能源转换效率和系统可靠性[5,6]. GaN在高频、高功率应用中展现了极大的潜力, 已经成为5G基站、雷达系统、快充技术等领域的首选材料, 推动了通信和消费电子的技术升级. 超宽禁带材料, 如氧化镓(Ga2O3), 由于其更高的禁带宽度和优异的抗辐射性能, 正逐渐受到研究者的关注, 未来有望在航空航天、核能设备和极端环境下的高压器件中得到广泛应用[7]. 超禁带宽度金刚石(diamond)是一类具有非常宽禁带宽度的金刚石材料, 通常指的是具有带隙大于 5.5 eV 的金刚石, 在高功率、高频率、耐高温和极端环境下的应用中, 表现出卓越的潜力[8].

宽禁带和超宽禁带材料不仅局限于提升功率器件的性能, 还推动了半导体技术的系统性创新. 例如, 结合这些材料的特性, 研究人员正在探索更高效的异质集成技术, 将宽禁带半导体与硅基电路、光电子器件以及射频电路相结合, 从而实现功率控制、通信和光电转换的一体化. 这种多功能集成能够显著提升系统的性能和效率, 适应未来量子计算、人工智能、6G通信等前沿技术的需求.

总之, 宽禁带和超宽禁带半导体材料为电子器件的发展带来了新的机遇. 这些新材料突破了传统硅基技术的局限, 特别是在高功率和高频应用中, 提供了前所未有的性能优势. 随着材料生长工艺和器件制造技术的进一步成熟, 宽禁带半导体有望成为未来半导体技术的重要支柱, 推动半导体产业在电力电子、通信、光电器件等多个关键领域的创新与发展.

1.1.3 二维材料

二维材料凭借其独特的电子、光学和力学特性, 逐渐成为推动新一代半导体技术发展的核心材料. 这些材料因其原子级的薄度和高度可调性, 在纳米尺度下展现了卓越的性能, 突破了传统半导体材料的物理极限, 尤其在微型化、集成化和高效能应用领域具有重要潜力. 二维材料的独特性质使其成为填补摩尔定律放缓所带来的技术空白的关键技术路径, 并为未来的电子器件、光电器件以及量子计算等前沿领域提供了创新的解决方案[9,10].

石墨烯是二维材料中的代表性材料, 因其卓越的电子迁移率、超高强度和优异的热导性, 在众多领域展现出广泛应用前景[11]. 然而, 石墨烯缺乏带隙限制了其在传统开关器件中的应用, 尽管如此, 通过对石墨烯结构进行改性或与其他半导体材料(如硅、二硫化钼等)进行异质集成, 研究人员已成功调节其带隙, 使其在低功耗、高速电子器件中展现出巨大的应用潜力. 这种石墨烯基复合材料不仅为半导体器件的性能提升提供了新途径, 也为未来集成电路和柔性电子等领域的创新提供了可能. 过渡金属二硫化物(transition metal dichalcogenides, TMDs), 如二硫化钼(MoS2)

, 在二维材料中同样占据了重要地位. 凭借其可调带隙和优异的电子特性, MoS2已在高效能场效应晶体管(field effect transistor, FET)和光电子器件中取得显著进展[12,13]. MoS2在单层状态下表现为直接带隙材料, 使其在光电探测器和光电子器件中的应用具备巨大的潜力. 与石墨烯不同, MoS2具备优异的开关性能, 因此在FET中展示了与硅基器件竞争的性能. 更为重要的是, MoS2的带隙可以通过外部应力、化学掺杂或异质结构调节, 极大地拓宽了其在柔性电子、光电集成电路和高速通信等领域的应用前景.

此外, 其他二维材料如黑磷和氮化硼也在超越摩尔时代的半导体应用中引起了广泛关注. 黑磷凭借其各向异性和可调带隙, 在电致发光、光电探测以及量子计算等领域表现出独特优势[14]. 氮化硼则以其高热稳定性和出色的电介质强度, 在高频、高功率和高温应用中具有重要的潜力, 尤其在作为绝缘材料或热管理材料的应用中展现出独特优势[15].

综上, 二维材料在超越摩尔时代的半导体新材料研究中具有重要意义. 这些材料突破了传统半导体技术的局限, 推动了电子器件和系统的多样化发展, 尤其在量子计算、柔性电子、光电集成电路和高速通信等新兴领域中具有巨大的应用潜力. 随着二维材料的制备工艺和性能优化的不断进展, 预计它们将在未来的半导体产业中发挥越来越重要的作用, 为下一代电子技术的创新提供强有力的支撑.

1.2 超越摩尔时代的半导体新器件

在超越摩尔时代的进程中, 研究者们正在探索新的材料、新结构和物理机制实现新型器件, 以推动微电子和光电子领域的革新. 探索了化合物半导体材料实现的新型器件, 如GaN等宽禁带半导体材料, 凭借卓越的电学和热学性能, 广泛应用于高功率、高频率及光电子器件中, 推动了5G通信和高效能LED的技术发展. 射频器件和功率电子器件的进步, 使得信号处理和能量管理更加高效, 推动通信与计算系统的同步升级. 量子材料、铁电材料与自旋材料为量子计算、存储器件和自旋电子学提供了关键支持, 提升了器件的计算速度和存储密度. 通过异质集成技术和多功能材料的组合, 这些新器件使得集成电路能够在同一芯片上高效协同工作, 为“超越摩尔定律”提供了核心支撑, 推动半导体技术和计算系统的发展, 支撑大数据时代对算力、存储、数据传输和电源管理等多方面的需求.

1.2.1 微电子领域

(1)集成自旋量子比特. 在摩尔定律已经接近物理极限的情况下, 寻找可以超越摩尔定律的方案是目前紧迫的问题. 基于量子力学原理的量子计算机具有比传统计算机指数级更快、更精确进行数据处理和计算的能力[16]. 在众多实现量子计算的途径中, 利用电子自旋来代替电荷加载信息实现大规模量子计算, 目前已经成为超越摩尔定律的一种重要候选方案和技术路线[17]. 利用硅基半导体实现量子计算[18], 具有和现有成熟的硅基半导体产业工艺兼容、可集成性和可扩展性、量子退相干时间长[19]、操控保真度高[20]等突出优势和优点, 已经成为量子计算研究的核心方向之一. 最近几年, 国际上基于硅基自旋量子比特的量子计算发展迅速, 量子比特数每年都实现了翻倍, 最近报道实验室已经实现10个量子比特的逻辑操控和调控[21]. 因此发展实用化的硅基量子计算机已经成为多家美国国家实验室和国际半导体公司实现超越摩尔定律的重要方向, 欧盟已经制定欧洲量子旗舰计划统筹欧洲的量子技术工业和研发计划, 全面推进量子技术发展.

基于硅基的自旋量子比特需要将电子/空穴限制在硅衬底上的量子点中, 例如硅金属氧化物半导体(metal oxide semiconductor, MOS), Si/SiGe异质结, Ge/SiGe异质结等结构[22]. 在众多方案中, 由于锗空穴具有有效质量小、易于制备、能谷劈裂大、自旋轨道相互作用强等特殊优势, 利用锗空穴的硅基集成自旋量子比特计算得到学术界和产业界的广泛关注[23]. 考虑到锗空穴, 特别是在半导体量子点系统中[24], 拥有强的自旋–轨道耦合效应(spin-orbit coupling, SOC)[25], 2019年实验上使用结构简单的全电自旋操控的方式实现锗空穴自旋的快速操控[26]. 随后在此基础上, 基于锗空穴自旋量子比特数每年翻一番[21,27]. 因此硅基锗空穴自旋量子比特已经展现出实现全电控量子比特操控与可扩展性的重要能力, 为实现硅基半导体量子计算并最终搭建大规模集成的通用量子计算机奠定了重要研究基础.

(2)宽禁带半导体功率器件. 宽禁带半导体功率器件(WBG power devices)是基于具有较宽禁带宽度的半导体材料(如氮化镓(GaN)、碳化硅(SiC)、氮化铝(AlN)、金刚石等)制造的电力电子器件. 这些材料具有优异的电气、热学和机械性能, 使得它们能够在更高的电压、更高的频率、更高的温度以及更恶劣的环境下工作, 进而大幅提高功率转换效率和可靠性[28,29]. 宽禁带半导体电力电子器件是电动汽车、AI算力中心、新能源发电、工业电机等领域实现电能高效转换利用、助力“双碳" 目标实现的革命性技术. 宽禁带半导体功率器件在电动汽车(electric vehicles, EV)的驱动系统、电池充电器和电力电子转换器中具有广泛应用. SiC MOSFET 和 SiC 二极管被广泛用于高效的电动汽车驱动系统和快速充电系统中. 在可再生能源系统中, 宽禁带半导体功率器件能够提高电力变换效率, 并在更高温度下稳定运行. 例如, SiC MOSFET 可应用于太阳能逆变器中, 实现更高效的能量转换. 用于工业设备中的电力电子系统, 如电源转换器、调速器、焊接机等. SiC 和 GaN 功率器件的高效率、高可靠性和宽工作温度使其非常适用于这些应用. 在极端温度、高辐射环境和高功率要求的航天和军事应用中, 宽禁带半导体器件因其卓越的抗辐射能力、高温稳定性和高功率承受能力而受到青睐. 此外, SiC 和 GaN 功率器件能够提高电网的效率和稳定性, 尤其是在智能电网的电力调度、能源储存和配电系统中.

宽禁带半导体电力电子器件向更高压、更低压、更高功率、更高集成度方向发展. 高压器件方向, 蓝宝石基GaN高压器件得到快速发展. 6∼8英寸8000 V蓝宝石基GaN高压器件取得突破, 推动全球GaN电力电子技术迈入1200 V以上高耐压、大尺寸、低成本8英寸时代. 低压器件方向, 重点突破低压器件三维集成技术, 提供大电流高效率电压电源, 同时, 突破15 V以下低压GaN功率器件, 为算力应用奠定基础. Intel基于300mm/0.18um工艺实现的GaN技术和 Si CMOS驱动技术展示出低压GaN功率器件在5∼15 V仍具有显著的大电流优势. 分布气隙磁性元件的三维负载点(point of load, PoL)转换器电路结构, 实现更低寄生参数、更高效率和优异的散热性能的GaN低压电路, 12转1.8 V电源效率达90% 电流高达35∼70 A, 显示出GaN电源大电流、高效率的明显优势. 在高功率方向, 中国处于领先地位, 突破了超薄外延层、新型异质结构、金刚石衬底等技术[30,31]. 氧化镓电力电子器件研究近年来实现了快速发展, 国内多家科研单位在氧化镓功率器件研究处于国际前列, 实现8000 V、击穿场强高于6 MV/cm的性能指标. 功率集成方向, Si/GaN混合CMOS和GaN单片CMOS均已实现突破.

(3)宽禁带半导体射频器件. 宽禁带半导体射频器件(wide bandgap semiconductor RF devices)利用宽禁带材料在射频(radio frequency, RF)和微波频段内实现更高效的信号放大、转换、处理和传输. 宽禁带半导体由于其优越的高功率密度、高频率响应、低损耗和高效率特性, 广泛应用于无线通信、雷达、卫星通信、5G及6G通信、射频放大器、射频开关等多个领域. GaN被誉为机载雷达自有源相控阵技术革命以来最大的一次性能飞跃. GaN是5G通信领先的核心技术. 宽禁带半导体射频器件将是未来很长时期引发5G/6G/卫星通信、雷达/对抗/微波武器等领域发展的革命性技术.

宽禁带半导体射频器件主要沿着更高功率、更高频率、更高集成方向快速发展. 在高频率方向, 美国处于领先地位, 通过N面HEMT突破120∼150 GHz功放和低噪放, 通过Ga面AlN/GaN HEMT突破162∼217 GHz功率放大器, 而且已实现GaN、硅CMOS、InP和GaAs三维异构集成[32-34]. 氧化镓Ga2O3射频晶体管已实现2 GHz下输出功率密度3.1 W/mm, 功效PAE 50.8%的突破[35-37]. 同时, 氢终端金刚石射频晶体管已实现2 GHz下输出功率密度4.2 W/mm的突破. 新材料方向, 中国和日本处于领先地位, 金刚石射频器件持续发展. 氢终端金刚石射频晶体管已实现2 GHz下输出功率密度4.2 W/mm的突破[38,39].

1.2.2 光电子领域

(1)硅基光电子器件. 硅基光电子器件主要包括硅基集成激光器、光调制器以及探测器等. 硅基集成激光器的研究主要集中在突破硅的间接带隙特性, 以实现高效的光发射. 传统上, 硅由于其带隙性质, 无法自发发射光, 因此光源的开发必须依赖于III-V族半导体材料(如InGaAs, GaAs)或氮化物材料(如InGaN)的异质结构集成[40]. 这些异质结构有效地弥补了硅的光学增益不足. 目前, 将III-V族材料集成到硅衬底的集成方案主要有3种: 混合集成(hybrid integration)、基于晶圆键合的异质集成(heterogeneous integration)和基于直接外延生长的单片集成(monolithic integration)[41-43]. 例如, 硅与InGaAs的异质结的集成, 利用外延生长技术, 能够增强光输出并提高光电转换效率. 在硅基氮化物材料方面, InGaN作为一种直接带隙材料, 其集成被广泛研究,特别是在高效发光和宽光谱调谐性方面展现出强大的潜力. 2016年 Nature Photonics 报道了Si基异质外延InGaN激光器[44]. 近年来, 量子点技术也在硅基激光器的开发中取得了重要进展,能够在较低电流下产生高光输出, 且减少热损失. 2016年 Nature Photonics 报道了电注入Si基外延InAs/GaAs量子点激光器[45]. 美国加利福尼亚大学圣巴巴拉分校(University of California, Santa Barbara)、IBM和IMEC等科研机构的研究成果在硅基激光器的集成化和功率提升方面作出了重要贡献[41-43]. 2025年 Nature 报道了与300 mm CMOS兼容的 Si基外延GaAs激光器[41]. 未来, 硅基激光源将进一步朝向低功耗、高效率、高集成度的方向发展, 推动光通信、量子计算和智能传感器等技术的进步.

硅基光调制器是硅光子学平台中的关键器件, 负责将电信号转换为光信号, 从而在光通信系统中实现数据的高速传输. 近年来, 基于电光效应的Mach-Zehnder干涉调制器(mach-zehnder modulator, MZM)和微环调制器(micro-ring modulator)已成为硅基光调制器的重要发展方向[46,47], Mach-Zehnder调制器利用硅的高折射率差异进行调制, 具有较低的插入损耗和较高的调制速率. 硅基调制器的高集成性和较低成本, 使其在数据中心、高速网络和光互联等领域具有广阔的应用前景. 例如, Intel和IBM在其光互联技术中使用了基于硅平台的光调制器, 显著提升了数据传输速率并降低了能耗. 未来, 随着光通信系统对更高速率和更低功耗的需求增加, 硅基光调制器将持续向更高的调制速率、更低的功耗及更紧密的集成方向发展. 为了满足5G、数据中心和超高速互联网的需求, 硅基光调制器将在大规模集成和低成本制造方面继续取得重要突破.

硅基探测器在光通信系统和传感器技术中具有至关重要的作用. 硅作为一种广泛使用的半导体材料, 其高效的光电转换能力使得硅基探测器在光通信中的应用得到了迅速发展[48,49]. 硅基探测器包括PIN光电二极管(positive intrinsic negative photodiode)和雪崩光电二极管(avalanche photodiode, APD), 其中, PIN光电二极管因其简单结构、低成本和高效率被广泛应用于光通信系统中. 硅基APD探测器, 凭借其较高的增益特性, 能够提供更高的灵敏度, 并适用于长距离光通信系统. 在这一领域, 科研机构如麻省理工学院和硅光子学企业Optalysys等, 正致力于开发更高性能的硅基探测器, 特别是在量子通信和高精度传感等领域的应用. 例如, 量子点掺杂的硅基探测器正被用于量子密钥分发(quantum key distribution, QKD)和量子信息处理的系统中, 增强了其在低温和低信噪比环境中的性能. 未来, 硅基探测器将朝着高灵敏度、低噪声、宽光谱响应和快速响应等方向发展, 拓展其在量子通信、医疗传感器和环境监测等领域的应用. 随着量子计算和量子通信技术的快速发展, 硅基探测器在未来的量子信息科技领域将发挥更为重要的作用.

(2)微型发光二极管(Micro-LED)集成技术. Micro-LED集成技术的发展主要集中在高效异质集成、光电互连和功耗优化等方面[50-59]. 在Micro-LED与CMOS驱动的集成显示技术中, Micro-LED与Si基CMOS的异质集成已成为虚拟现实(virtual reality, VR)、增强现实(augmented reality, AR)和抬头显视设备(head-up display, HUD)等微显示应用的主流方案[52,53]. GaN基LED与高电子迁移率晶体管(high electron mobility transistor, HEMT)或MOSFET的同质集成技术, 可有效降低驱动功耗并提高像素密度[57,58], 这对大尺寸显示和高精度图像处理领域具有重要推动作用. 深紫外Micro-LED的微型化也正在促进无掩模光刻技术的发展, 助力降低芯片制造成本[59], 但进一步提升光刻分辨率仍是未来的技术需求. 深紫外Micro-LED的集成在未来光学制造和高精度加工领域将具有广泛应用前景.

在应对超越摩尔时代的人工智能应用算力需求增长中, 光电互连与低功耗数据传输起到至关重要的作用. Micro-LED作为光电互连的重要器件, 具有替代传统电互连的潜力. 相比电互连, 光电互连不仅能降低功耗, 还能显著提升数据传输速率, 特别适合应用于数据中心和高性能计算系统[60]. Avicena公司提出的双向总带宽超过1 Tbps、功耗低于1 pJ/bit的解决方案, 表明Micro-LED与CMOS IC结合的低功耗高速光电互连技术是应对AI模型高算力需求的关键路径. 在通信领域, Micro-LED的短距离高速数据传输能力使其在6G时代有望成为射频通信的有力补充. 基于Micro-LED的可见光通信(visible light communications, VLC)技术具有高速、低延迟等优势, 能够解决射频通信频谱资源紧缺的问题[61]. 随着Micro-LED技术的不断优化, VLC将在未来的室内无线通信和车联网等领域得到广泛应用. 最后, 在光电集成电路与光计算方面, Micro-LED与半导体器件的集成推动了光电集成电路的发展[62]. 该集成方式将光学功能嵌入电路中, 形成光电混合电路, 应用于光计算和光传感等领域. 该光电集成电路有望突破摩尔定律的限制, 推动新型计算架构的发展, 特别是在人工智能和高性能计算等需要高速并行处理的领域中. 随着关键技术的不断突破, Micro-LED有望成为下一代显示和通信的核心技术之一.

1.3 超越摩尔时代的体系新架构

新体系架构是推动算力提升的关键因素. 超越摩尔时代的体系架构不再局限于单一的集成架构, 而是转向更加灵活和高效的多层次、多功能的同质/异质集成架构. 光电集成技术、光子集成以及混合集成架构通过集成不同的功能模块, 能够显著提升数据的传输效率和系统的整体性能. 实现不同器件平衡发挥, 突破节点瓶颈.

1.3.1 光电异质融合集成新架构

随着人工智能(artificial intelligence, AI)时代的到来, 数据中心对算力的需求呈指数级增长, 现有计算架构难以满足这一需求, 迫切需要发展突破摩尔定律限制的新一代计算架构, 推动计算模式从单核向多核及分布式演变[63,64]. 同时, 这一变革对计算数据的采集、通信和处理提出了更高的要求. 受限于功耗墙、存储器与单芯片面积墙, 单核算力增长遇到物理极限. 传统单核处理器在面对复杂计算任务时, 其性能提升受到晶体管尺寸缩小的物理限制, 难以通过简单增加单位面积晶体管数量来提升计算能力[65]. 因此, 处理器从单核发展到多核, 通过集成多个核心来提高并行处理能力, 以满足日益增长的计算需求[30,31]. 然而, 多核处理器在处理大规模并行任务时, 仍面临核心间通信延迟、数据共享等问题, 难以充分发挥多核的潜力. 因此, 分布式计算成为发展趋势[66]. 分布式计算通过将计算任务分解为多个子任务, 分配到多个计算节点上并行处理, 从而实现计算能力的扩展. 这种架构能够有效解决单核和多核处理器在处理大规模数据时的性能瓶颈问题, 为AI训练、大数据分析等需要海量计算资源的应用提供了可行的解决方案[67]. 这为数据采集/通信/处理提出了新的要求. 数据采集方面, 需要更高效的传感器和数据采集设备, 以快速、准确地获取大量数据[68]. 通信方面, 要求数据传输速度更快、带宽更宽, 以满足分布式计算节点间大量数据交换的需求[69]. 处理方面, 则需要更先进的数据处理算法和软件架构, 以实现对海量数据的高效处理和分析[70].

光接口是大规模分布式计算的重要选择之一[71]. 光接口具有传输速度快、带宽大、抗电磁干扰能力强等优点, 能够有效解决传统电接口在高速数据传输时面临的功耗高、信号衰减严重等问题. 芯片接口带宽每三年翻一番, 这得益于光接口技术的不断进步和创新[72]. 在光电融合过程中, 传统的电控–电算–电传处理体系开始向电控–电算–光传异质系统转变, 通过光电系统集成, 硅光芯片集成规模不断增加, 能够实现更高速率的数据传输和更复杂的光信号处理功能[73]. 关键技术包括面向光互连与光接口的高性能器件, 研究重点是阵列化高性能单元. 阵列化高性能单元能够实现大规模的光信号并行处理, 提高系统的整体性能和效率. 目前, 单元器件的性能瓶颈是制约硅光集成规模持续增长的主要因素, 发展近零相位误差的器件将显著推动大规模光电融合系统的发展[74].

在关键核心技术发展方向上, 重点发展了高性能的光电子单元器件, 以支撑更大规模的片上集成, 包括窄线宽/多波长激光器、宽频带低功耗高线性电光调制器及阵列、超宽带超高灵敏度光电探测器、灵活可调的片上光信号处理单元和低损耗低功耗的光互联接口等关键器件[75]. 这些高性能器件能够满足分布式计算对高速、大容量数据传输和处理的需求, 提升整个系统的性能和效率. 另外, 充分挖掘和利用不同材料体系的优势, 如硅基、III-V族半导体、铌酸锂、钽酸锂、低维材料、宽禁带半导体等, 通过多材料体系的融合集成, 充分发挥各种材料的独特性能和优势, 推动计算系统向高速率、低功耗、小型化和智能化方向发展, 为新一代信息技术和人工智能技术的升级提供强大支撑[76]. 例如, 硅基材料具有良好的集成性和成本优势, III-V族半导体具有优异的光电性能, 低维材料,如石墨烯,具有高迁移率和低功耗等特性. 将这些材料有机结合, 能够实现更高效的光电集成和更先进的计算架构, 为新一代信息技术和人工智能技术的升级提供强大支撑.

当前, 高速数据传输导致电能的消耗急剧增加, 未来面向光互连的低功耗、高传输速率的氮化镓(GaN)集成光电子芯片领域将有望提供支撑. 此外, 宽禁带半导体器件的工作波长较短, 与现有的通信系统存在差异. 尽管围绕宽禁带半导体材料体系的蓝光通信已取得显著进展, 但由于工艺和体系的不成熟, 氮化镓的性能尚未达到硅的水平. 作为光电融合的基础, 化合物半导体在这一领域展现出广阔的应用前景. 从应用角度来看, 光通信也面临着诸多挑战, 例如需要数据缓存以确保数据的准确性, 这会对系统的成本产生影响. 因此, 需要从体系架构和底层器件两个层面进行协同创新, 以解决这些问题.

1.3.2 存算一体芯片架构

过去20年中, 主流处理器的算力每两年提升3倍, 而DRAM与互联总线带宽则每两年只增长1.4∼1.6倍, 访存延时成为计算瓶颈, 称为“存储墙”[77,78]. 随着大语言模型(large language model, LLM)等AI技术的迅速发展, 在模型训练过程中, 需要存储和访问海量参数, 因此, 高性能计算芯片面临的存储墙问题变得更加突出. 同时, 受制于DUV/EUV光刻机的掩模尺寸, 单芯片可制造的最大面积为26 ×33 = 858 mm2[79]. 近5年来, 面向高性能计算的GPU芯片单芯片面积基本维持在820 mm2左右, 通过集成电路工艺的尺寸微缩实现性能提升, 目前这一路径遇到了物理瓶颈[80]. 因此, 急需发展新技术突破算力进一步提升所面临的局限性. 现在的发展趋势是通过先进封装实现更高的存储密度、带宽和能效[81-83], 这需要解决三大关键问题: 多器件多芯粒异质集成的兼容性问题[84], 通过结合来自不同材料、技术和功能的多种器件和芯粒, 可以实现优异的性能和功能, 但由于不同材料的热性能和制造工艺等存在差异, 异质集成面临着一些兼容性问题亟待解决; 异构存算一体架构的设计与实现[85], 通过将数据存储和计算能力紧密结合, 实现更高效的数据处理, 在设计与实现上需要综合考虑多个因素, 包括系统架构、数据管理、计算模型和集成技术; 多工艺融合的存算一体芯片自动化设计理论[86], 随着包含多个不同功能的芯片被集成到单个封装中, 系统固有的复杂性和密集连接性在使用传统电子设计自动化 (electronic design automation, EDA)工具进行封装设计和组装制造验证时带来了重大挑战. 此外, 随着基于芯片的设计从单个单片芯片过渡到多芯片配置, 与分别规划和执行 IC 和封装布局设计的传统方法相比, 有效规划、管理和优化顶层设计和连接性以实现芯片间的最佳性能、功耗和面积 (performance power area, PPA)变得越来越具有挑战性和复杂性. 此外, 三维异质集成使得热管理和供电成为必须要解决的关键挑战[87], 随着处理器的算力持续提升, 处理器所需电流上升至数百安培, 这为供电网络的电压降(IR-drop)以及功率损耗提出了极度苛刻的设计要求, 也使得电源/信号完整性设计成为巨大的挑战. 基于异质异构芯粒的集成芯片是芯片设计的新范式, 关键技术包括: RISC-V多核处理器芯粒设计与集成以及容错片上网络设计, 但也存在“芯粒税”的挑战, 即将单一芯片划成芯粒后, 芯粒间的互连与通信成本不可忽略. 综合考虑, 集成芯片将给存算分离的计算架构带来设计范式的变革, 为处理器芯片存储层次重构提供新机会.

针对存算一体的底层技术层面, 硅基存储器件存在性能瓶颈, 电荷传输机制存储器, 包括SRAM, DRAM和Flash, 均存在速度与数据保持无法同步优化的难题, 这也是计算架构中层次化存储的物理根源. 为解决该难题, 极化、自旋、二维、氧化物等新材料有望带来底层机制突破[80,81,88], 突破硅基存储器速度、保持和大规模集成难以兼容的问题. 新材料、新原理的存储技术尚存在一些关键科学问题和共性技术需要解决, 如, 材料和界面的不理想特性对器件性能的影响规律、Si基CMOS兼容的高密度集成技术等. 为此, 急需从材料、器件与集成层面展开深入研究以实现突破.

2 超越摩尔时代半导体集成中的关键科学技术问题

2.1 超越摩尔时代的半导体新材料方向

2.1.1 失配条件下半导体光电材料异质外延动力学和原子级界面构筑技术

应力调控与缺陷抑. 高质量材料是实现高性能器件的根本保障. 半导体材料通常采用异质外延技术, 外延层与异质衬底间的晶格和热失配将导致外延层翘曲严重、缺陷密度高[89]. SiC材料通常采用同质衬底生长, SiC衬底存在的微管缺陷、碳包裹体、晶型夹杂、位错等缺陷在外延过程中容易扩展到其上生长的SiC厚膜, 导致缺陷密度高、出现台阶聚集等问题. 当前, GaN材料从4英寸向6/8英寸、SiC材料从6英寸向8英寸过渡. 随着晶圆尺寸扩大, 外延晶片衬底应力大、外延生长设备反应腔体温场和气流场分布更为复杂, 上述问题愈加严重. 因此, 急需开展大尺寸衬底上外延生长动力学研究, 厘清应力产生机理和缺陷演变规律, 以发展应力调控方法, 实现低缺陷密度半导体材料外延.

高效p型掺杂. n/p型掺杂是实现宽禁带半导体器件功能的基本要素. 在III族氮化物半导体中, p型掺杂的实现面临显著挑战, 其难度远超n型掺杂. 以GaN为例, n型掺杂中Si施主的激活能仅为10∼20 meV, 而p型掺杂中Mg受主的激活能则高达约160 meV. 此外, 强烈的自补偿效应导致空穴浓度较电子浓度低1∼2个数量级. 这一问题在含Al组分的材料中进一步加剧: 随着Al组分的增加, Mg杂质替代Al或Ga原子的形成能显著升高, 使得高Al组分AlGaN中的Mg掺杂浓度极低. 同时, Mg受主的激活能呈线性增长趋势, 例如在AlN中可达465∼758 meV, 导致激活效率急剧下降. 因此, 随着Al组分的提升, III族氮化物的p型掺杂效率持续降低, 外延层电导率也随之迅速恶化. 因此, 高效p型掺杂成为宽禁带半导体光电器件发展的主要障碍之一, 也是该领域的国际难题.

原子级界面构筑. 界面陡峭、组分可调的多元混晶量子结构、异质结构是提高半导体光电器件性能的核心, 其特征尺度通常只有数纳米. 例如, AlN, GaN, InN 之间化学键能、晶格常数差异都很大, 是典型的生长温度和晶格双方面大失配系统, III族氮化物材料的生长制备通常需依赖非平衡条件, 其生长动力学过程极为复杂. 以适用于规模化生产的MOCVD (金属有机化学气相沉积)外延技术为例, MO源(金属有机化合物)的分解与预反应、衬底表面的吸附–迁移–解吸附行为均难以精确调控. 这一过程中, 不仅易发生相分离现象, 还会显著增加晶体缺陷的生成概率, 从而影响材料的结构完整性与光电性能. 因此, 如何实现原子级界面平整的量子结构/异质结构外延生长是发展宽禁带半导体技术的另一关键科学问题.

2.1.2 半导体光子–电子行为和相互作用机制及其调控方法

强极化体系载流子注入、输运、复合规律. 不同于传统的III-V族化合物半导体, 氮化物稳定的纤锌矿结构具有极强的自发极化和压电极化场. 该天然属性使其能带沿着极化的方向弯曲, 从而改变了传统量子结构的能带, 影响载流子注入、输运、复合过程. 例如, GaN基异质结中, 极化场能够增强量子限制效应、提高二维电子气(two-dimensional electron gas, 2DEG)的迁移率, 但同时将增加等效肖特基势垒高度, 影响电子的隧穿和输运过程; 而在InGaN等多量子阱结构中, 倾斜的量子结构能带使得阱中的电子和空穴分别向相反的两侧聚集, 电子和空穴的波函数在空间上发生了分离, 其辐射复合发光几率下降.

强限域量子结构电子、光子、声子相互作用和转化规律. 随着器件尺寸不断逼近极限, 半导体中微观粒子的动力学行为、粒子间相互作用将从经典过渡到量子. 量子阱、纳米线、量子点等强限域量子结构中, 电子在至少一个维度上受到空间束缚, 其态密度的增加将深刻影响光电耦合效率、电声子散射强度及载流子弛豫速率, 从而影响发光器件的量子效率、光电器件的响应速率及灵敏度. 此外, 强限域效应也将带来全新的光电器件, 如多量子阱结构可以实现光电耦合效率的协同提升, 从而为实现光–物质强耦合提供了可行的技术路径. 三维受限的量子点可提供固态环境中的二能级系统并发射单光子, 成为发展量子光源的重要体系. 半导体量子结构导带和价带带阶大, 量子限制效应增强和介电屏蔽效应减弱, 对外部调控极为敏感, 通过应变工程、光场调控等策略, 可精确控制材料的光子和电子行为, 有望大幅提高器件性能.

多界面低维体系光子的运动规律和行为调控. 半导体材料和器件中的光子在高折射率、多光学界面的环境下, 会发生全反射、光波导效应、界面反射与折射、光子散射以及光子吸收与再发射等现象, 对材料的光学性能和器件的性能具有重要影响. 例如, 介电常数交替变化的半导体或介质薄膜可构成布拉格反射镜, 进一步利用法布里–珀罗腔(Fabry-Perot), 将光子局域在微腔中心, 从时间和空间两个维度增强光电子相互作用, 从而将光电子相互作用的强度区间从弱耦合推广至强耦合, 实现器件物理从Purcell效应至极化激元的转变; 将多层量子阱结构加工刻蚀成光子晶体结构, 利用其光学衍射模式及导模的共振耦合, 可以实现光场的强局域, 同时保证极高的光学品质因子. 这一研究体系可以将拓扑光子学与半导体光电器件物理结合, 利用拓扑光子学的光场调控手段, 实现超高品质因子微腔、极低阈值激光、多维度场光电感知器件等高性能光电器件.

2.1.3 半导体材料多功能集成、材料兼容性与散热机制

(1) 多功能集成与材料兼容性. 在新的半导体技术中如何实现不同功能材料(如光电子材料、热电子材料和常规电子材料)进行集成, 解决不同材料间的界面匹配、热膨胀匹配以及电气性能的兼容性, 实现高效的多功能集成, 尤其是光电集成、光子–电子集成以及量子计算集成, 是一个关键科学问题.

(2) 高效能量转换与散热机制. 在微电子和光电子器件中, 热问题是限制器件性能和寿命的一个关键因素. 如何提高半导体材料的热管理能力, 依然是当前面临的重大科学挑战. 宽禁带半导体(如氮化镓、碳化硅)具有更好的热导率, 但依然存在如何有效散热的挑战. 设计热管理结构和散热材料, 提高能量转换效率, 以确保高功率器件在高温下稳定工作. 对于超越摩尔时代的半导体材料, 如何实现更高的能量转换效率, 尤其是在光电效应和热电效应方面, 是一个亟待解决的科学问题.

2.2 超越摩尔时代的半导体新器件

2.2.1 集成自旋量子比特方向

(1)硅电子自旋量子比特的能谷劈裂. 集成自旋量子比特面临的一个关键科学问题 是,如何提高硅电子自旋量子比特的能谷劈裂. 自旋作为电子的内禀自由度, 由于其可以提供对外界电场不敏感的二能级系统, 展示出了完美量子比特的最重要基本特性, 即可以长时间保持量子相干特性[17]. 近期科学界将布洛赫(Bloch)电子的能谷作为新的自由度进行调控[90]. 能谷指布洛赫电子能带的最高处或最低处, 如果材料中存在一系列简并或者接近简并的能谷, 通过掺杂以及应力调控等手段, 能谷可以劈裂成为分立的能级, 从而实现自旋量子比特的设计和制造[18]. 然而量子比特要求是简单的二能级系统, 也就是只需要一个谷的自旋向上和向下的态, 如果另一个谷能级靠得很近, 就会导致量子信息的泄露. 长期以来, 在Si/SiGe器件中较低的能谷劈裂阻碍了硅电子自旋量子比特的发展[91], 因此需要通过器件设计和优化在硅电子自旋器件中实现更大的能谷劈裂, 为集成自旋量子比特的发展提供材料学基础.

(2)全电控方式自旋量子比特的超快调控. 随着集成自旋量子比特的迅速发展, 寻找利用全电控方式实现自旋量子比特的超快调控, 是提升量子计算系统性能的关键科学问题. 大规模的量子计算要求对量子比特之间的耦合进行开或关的操作[17]. 在硅基量子点器件中, 可以通过自旋轨道耦合实现自旋与电偶极矩发生关联, 从而可以使用外电场来操控电子自旋, 比原本通过磁场来耦合调控得到简化[25]. 然而需要注意的是, 材料中的声子或者缺陷产生的偶极矩也会对自旋有影响, 从而在系统中产生噪声造成量子退相干. 另外, 由于目前硅基量子点中自旋轨道耦合效应仍然很弱, 如何实现超快、高效的全电自旋操控(electric-dipole spin resonance)量子比特[21], 是目前集成自旋量子比特发展的前沿关键科学问题.

(3)高迁移率锗空穴自旋量子比特材料. 集成自旋量子比特的实际应用, 需要获得高迁移率锗空穴自旋量子比特材料等. 由于硅自旋轨道耦合系数较小, 应用范围有限; 而锗的锗空穴有效质量小、自旋轨道耦合系数大, 易于实现高速的全电自旋操控[92]. 另一方面, 基于锗的栅控量子点可以做得很大, 便于实验上操作, 易于制备大规模可扩展性、高良率的量子点阵列[21]. 针对这一问题, 制备高迁移率锗空穴自旋量子比特材料, 并研究利用新型器件, 例如发展基于平面异质结的超快锗空穴自旋量子比特[93], 可以加速量子比特的大规模可扩展性的应用.

(4)大规模制备具有可扩展性、高性能的集成自旋量子比特. 大规模制备具有可扩展性、高性能的集成自旋量子比特仍然是实现量子计算的关键核心问题. 在材料方面, 由于制备出的硅基量子点不能确保良率, 造成量子比特的一致性问题[22]; 在器件方面, 由于量子点长程耦合性的存在, 当多个量子点紧密排布在一起时, 难以在其中排列布线进行互联[21]. 因此在技术层面制备具有高度可扩展性、高性能、高一致性的小型硅基自旋量子比特, 设计新型的纳米结构并确定合适的工作点, 实现大规模自旋量子处理器, 是实现基于硅基自旋量子比特的大规模集成通用量子计算机的关键核心问题.

2.2.2 宽禁带功率半导体与射频器件方向

(1)宽禁带半导体材料创新制备与性能提升. 材料创新与性能提升是驱动宽禁带半导体电子器件发展的根本驱动力. 宽禁带半导体材料如GaN和SiC, 在外延过程中容易产生缺陷和应力, 这些缺陷会显著影响材料的性能, 尤其是在功率与射频应用中的高效性和可靠性. 材料缺陷如位错、表面缺陷、掺杂不均匀等, 可能导致器件的漏电流、击穿电压降低, 甚至影响器件的寿命. 如何持续发展兼顾大尺寸、高质量、低成本的超宽禁带半导体(金刚石、氧化镓、氮化铝等)单晶衬底, 并进一步构筑宽禁带半导体(金刚石基氮化镓、碳化硅基氧化镓、金刚石基氧化镓等)材料复合结构满足高功率、高频率、高集成等不同器件最佳性能需要, 是宽禁带半导体电子器件面临的关键科学问题.

(2)超宽禁带半导体掺杂性能调控. 如何找到新型掺杂、新型异质结构等超宽禁带半导体(AlN/氧化镓P型掺杂、氧化镓异质结构、金刚石异质结构等)导电或二维载流子导电调控方法, 加速复杂结构宽禁带半导体材料的设计与制备迭代周期, 是宽禁带半导体电子器件面临的另一个关键科学问题. 在超宽禁带半导体材料(如AlN, Ga2O3, 金刚石等)中, 掺杂技术是调节材料电导性、控制载流子浓度及优化器件性能的核心技术. 然而, 由于这些材料本身的宽禁带特性, 掺杂过程通常面临效率低、热稳定性差、杂质引入等问题.

(3)器件集成工艺与可靠性. 器件集成工艺与可靠性是影响宽禁带半导体电子器件性能发挥与应用的关键. 如何构筑高性能、高可靠性的宽禁带半导体电子器件, 尤其是Ga2O3MOS、金刚石MIS等肖特基结和金属–绝缘体–半导体(metal-insulator-semiconductor, MIS)结构, 以及实现更低电阻的宽禁带半导体(如AlN, Ga2O3, 金刚石等)的欧姆接触, 是宽禁带半导体器件性能提升与应用的关键所在. 由于宽禁带材料的高带隙特性和本征缺陷, 如何在这些材料上实现低电阻、稳定性好且可靠的欧姆接触及肖特基接触, 仍然是一个复杂且具有挑战性的科学问题.

(4)宽禁带器件异质异构集成. 实现性能更优、结构更复杂的宽禁带半导体器件, 特别是通过异质纵向结构、同质或异质双极互补结构、超级结构以及三维异质异构集成等新型设计, 能够极大提升宽禁带半导体器件的性能, 并满足工业级、汽车级、宇航级等高可靠性应用需求. 然而, 面对更高的工作环境要求, 如何在满足高功率、高频、极端温度和辐射条件下实现可靠性和性能的平衡, 依然是当前面临的重大科学挑战.

2.2.3 硅基光电子器件方向

(1)低缺陷密度硅基III-V族半导体材料异质生长. 低缺陷密度硅基III-V族半导体材料异质生长是关键问题. 硅与III-V族半导体(如InGaAs, GaAs, InP, GaN)之间存在较大的晶格常数差异, 这种晶格失配往往导致外延层中形成大量的位错和缺陷, 这不仅影响材料的光学性能, 还会降低激光器的效率和稳定性. 如何有效缓解晶格失配带来的应力, 减少缺陷的生成, 确保外延层的光学质量, 如何通过设计优化缓冲层和过渡层, 使得外延材料能够在硅基底上生长出高晶体质量的III-V族半导体材料, 是硅基III-V族半导体材料异质生长的关键科学问题.

(2)增益介质优化以及器件可靠性. 硅基光电子器件结构中的增益介质优化以及器件可靠性难题. 增益介质的质量和设计直接影响激光器的输出功率、效率和阈值电流. 因此, 如何设计优化增益介质的光学特性, 如载流子复合率、发光效率、光学增益等高效的增益介质, 在硅基外延激光器中实现最大化的增益, 并优化掺杂技术、量子点技术或量子阱结构, 以提升激光器的增益特性, 是一个重要科学问题. 此外, 作为光子集成电路的核心部分, 集成片上激光器还必须确保能在温度范围较大的环境下稳定工作(30∘C∼150∘C)并拥有足够长的工作寿命. 因此, 如何实现高效的热管理和散热设计是硅基光电子器件发展的关键问题之一.

(3)硅基光电子器件高集成度与尺寸缩小. 硅基光电子器件集成度与尺寸缩小问题. 硅基光电子器件的一个重要优势是其可以与硅平台高度集成. 然而, 集成度的提高通常意味着器件的尺寸需要进一步缩小, 引起热管理、电气隔离、光学耦合等问题. 如何在不牺牲光电子器件性能的前提下, 在硅平台上实现多功能光电子器件的高效集成, 进一步缩小尺寸并提高集成度, 是硅基光电子器件面临的重要挑战.

2.2.4 Micro-LED集成技术方向

(1) Micro-LED光电互连器件. 光电互连技术是Micro-LED在通信和计算应用中的核心问题之一, 如何实现Micro-LED作为高速数据传输和低功耗光电互连的器件, 并提升其传输速率和信号完整性, 是超越摩尔定律下的计算架构革新中一个关键问题. 在光电互连中, Micro-LED不仅需要提供足够的发光强度, 还需保证信号在传输过程中的完整性, 避免因信号衰减、畸变和串扰等问题导致数据错误或传输效率低下. 作为高速数据传输器件, Micro-LED需要具备高速调制能力和稳定的光输出. 通过优化光电转换效率和调制频率(例如高频调制以适应高带宽要求), Micro-LED可以有效地支持高速数据传输. 改进电流驱动和调制技术, 尤其是引入更高效的调制机制(如脉冲宽度调制和调制深度调制), 能够进一步提升数据传输的速率.

(2) Micro-LED与驱动的异质集成. Micro-LED器件需要与薄膜晶体管(thin film transistor, TFT)或CMOS驱动电路进行异质集成, 如何实现高密度、高效的异质集成是关键挑战. Micro-LED显示作为下一代高分辨率、低功耗的显示技术, 正逐渐成为AR/VR、电视、智能手机等领域的关键技术. 要将Micro-LED集成到现有的计算架构中, 特别是实现与其他电子元件的兼容性, 需要高效的封装和集成技术. 例如, 采用硅光子技术将Micro-LED与硅基集成电路(integrated circuit, IC)结合, 不仅可以提升集成度, 还能实现与现有CMOS技术的兼容. 这不仅要求Micro-LED芯片本身具有极高的亮度、色彩和分辨率, 还需要与外部驱动电路(如TFT或CMOS电路)进行高效的异质集成, 以实现精确的像素控制、快速响应和低功耗. 因此, 在集成设计中, 光学模块的布局、对准精度以及热管理技术都是需要重点考虑的因素.

(3)高效率红光Micro-LED器件. 针对Micro-LED全彩化中的红光效率低难题, 需要创新设计器件和集成方法实现Micro-LED显示集成中低功耗及高密度显示. 如何选择合适的材料系统(如InGaN, AlInGaP等), 在外延生长过程中, 如何解决InGaN红光发光量子阱中的应力、晶格不匹配和缺陷等问题, 是解决红光缺陷的关键科学问题. 在Micro-LED高密度集成和全彩化显示中, 如何在保证显示效果的同时进一步降低功耗, 成为关键挑战. 尤其是在高密度Micro-LED阵列中, 由于每个像素都是独立的发光单元, 如何有效地降低整体功耗并提高能效, 提升Micro-LED的稳定性和性能, 是当前器件设计的重点问题.

2.3 超越摩尔时代的半导体新架构

2.3.1 光电异质融合架构方向

(1)精确控制光电功能材料的生长与调控. 光电异质融合集成面临的另一个重大挑战是如何精确控制光电功能材料的生长与调控, 以满足不同光电器件的需求. 特别是大尺寸光电薄膜材料的可控生长对于实现高效集成至关重要. 首先, 必须研究材料的生长机制, 精准控制其厚度、结构与成分, 以确保不同材料之间的晶格匹配与界面质量[94]. 异质集成技术, 例如通过键合或外延生长, 将不同材料(如化合物半导体与硅基芯片)集成在一起, 能够充分发挥各自的优势, 提升集成系统的性能[95]. 然而, 材料间的界面应力、缺陷以及相容性问题仍需解决. 因此, 开发新型的表面分析技术和精准的表面处理技术, 优化光电材料的界面结构, 是实现高效光电融合集成的关键. 此外, 多材料系统的流片平台建设, 尤其是集成III-V族材料、硅基材料和二维材料等, 将促进不同光电材料和工艺的协同创新, 提高研发效率和产品质量.

(2)微观尺度上多维度物理参数调控. 光电异质融合集成技术的一个关键科学问题是如何在微观尺度上调控多维度物理参数, 以实现高效的光电协同转换. 光电系统中, 光子的波长、幅度、相位、偏振等特征与电场的空间、时间、幅度等维度相互作用, 直接影响光电转换效率及信号传输质量[96]. 然而, 现有的理论框架尚未能够系统地描述这些多维度参数在光电器件中的综合调控机理. 具体来说, 如何通过调整光场与电场的相互作用, 提升光电性能并突破传统器件的物理极限(如光波导的尺寸、探测器的响应速度等)是当前研究的重点[97]. 例如, 光波导的尺寸常受到光衍射极限的制约, 且传统器件的光电转换效率与响应速度往往受到材料特性与尺寸的制约. 通过深入研究多维度物理参数调控理论, 可以在纳米尺度上精细调控光电器件的设计, 突破现有的性能瓶颈, 为高效光电异质融合集成芯片的开发提供理论支持.

(3)跨尺度地优化光电功能结构. 随着光电异质融合集成技术的不断发展, 如何跨尺度地优化光电功能结构成为提升系统性能的关键问题. 在高密度集成的光电芯片中, 光、电、热等物理场的相互作用不仅影响光电转换效率, 还会导致信号传输的串扰[98]. 因此, 研究不同物理场之间的相互作用机制, 优化材料与器件结构, 是提高光电融合集成效率的重要途径. 特别是在光电探测器中, 通过优化光吸收层和载流子传输层的厚度与界面结构, 可以显著提高光生载流子的产生与传输效率, 降低复合损耗, 从而提升探测器的灵敏度和信噪比. 与此同时, 在高密度集成芯片中, 如何避免不同光电模块之间的串扰, 开发有效的抑制技术, 成为了确保系统稳定性的一个重要方向[99]. 研究优化波导布局、增加隔离层、采用热管理技术等, 能够有效提高信号传输的准确性和光电系统的整体性能.

(4)低损耗波导和高效信号耦合. 光电异质融合集成中, 波导设计和信号耦合是影响系统性能的关键因素. 波导作为光电器件的核心组件, 其设计优化直接决定了光信号的传输效率. 在集成系统中, 低损耗波导的设计至关重要, 这需要对波导材料、结构及尺寸进行精确优化[100]. 例如, 硅基波导、氮化硅波导以及薄膜铌酸锂波导等新型材料的应用, 为低损耗光信号的传播提供了更多选择. 在此基础上, 如何设计高效的耦合机制也是一个不可忽视的问题. 光电信号的高效耦合技术能够显著提高光电器件之间的相互连接效率, 减少光信号的损失[101]. 针对这一问题, 研究新型耦合器件, 如高精度对准技术、非接触式耦合技术等, 是实现光电信号高效转换和传输的关键. 这些优化措施不仅能提升光电集成芯片的集成度, 还能提高整体系统的性能, 满足高速、高带宽的应用需求.

高可靠集成与封装. 随着光电异质融合集成技术的发展, 光电器件的封装技术与高功率光电器件的性能优化成为了实现高效集成的难点之一. 尤其是对于高功率光电器件, 如何有效管理热量、减少噪声并保证长期稳定性是面临的主要挑战[102,103]. 研究高频电学特性和热噪声的产生机制, 优化光电器件的热设计, 是提升高功率光电器件性能的关键. 例如, 通过分析高功率器件的热噪声特性和光响应特性, 研究抑制热噪声的方法, 能够有效提升器件在高温环境下的稳定性和寿命. 在封装方面, 如何精准提取封装中的寄生参数, 优化封装结构, 减少串扰及损耗, 进一步提升光电信号传输的效率, 也是重要的研究方向[104]. 尤其是在高功率应用中, 研究互连集成与热管理方案的创新, 将有助于提升系统的可靠性和抗干扰能力, 确保光电融合集成芯片能够在复杂环境下高效稳定地运行.

2.3.2 存算一体集成架构方向

(1)材料–器件–电路–系统的全层级协同设计. 首先, 随着新原理、非易失存储器件的制备渐渐趋于成熟, 基于新型存储器的存算一体电路与芯片不断发展, 但如何在能效与计算精度之间取得平衡问题, 一直是学术界和产业界关注的关键科学问题[105]. 一般而言, 模拟存算一体具有高能效特点, 但受限于新器件的制造良率与非理想因素, 导致计算精度受限, 另一方面, 数字存算一体能实现高精度, 但是能效优势不显著. 为此, 需要从材料–器件–电路–系统的全层级协同设计, 以获得整体的最优解决方案. 在材料方面, 需要通过掺杂、热处理、界面工程、薄膜均匀沉积等方法, 减少器件在电学特性和物理特性上的随机扰动, 提高器件间一致性, 此外, 一些前沿的材料或低维结构(如二维材料、相变材料的新相态)有望提供更好的存储密度及模拟特性. 通过器件物理机理的深入研究, 使其在保持低功耗的同时, 仍能兼顾较高的计算精度. 存内计算常利用器件的多电阻态进行权值(权重)的存储与计算[106]. 如果要在能效与精度间平衡, 需要尽量提高模拟多态的可重复性和抗干扰能力. 在器件结构和操作脉冲设计上, 要保证编程线性度和抗随机游走能力. 在电路层面, 需要, 解决模拟存算一体的多值存储与计算问题, 以展现模拟存算一体的高计算效率和面积效率, 同时研究数字存算一体的定制化设计方法, 实现年存计算的性能优势. 在以上基础上, 为了兼顾存算一体电路设计的精度与能效, 在同一系统中同时集成高能效模拟和高精度数字存算一体, 实现兼顾能效与精度的数模混合异构存算架构.

(2)多芯粒集成的软硬件协同. 为解决传统冯⋅诺依曼(von Neumann)体系所面临的“存储墙”和“功耗墙”瓶颈, “存算一体”新范式旨在从基础器件、计算原理和体系结构上协同创新, 突破“存算分离+亚10 nm 工艺”的智能计算系统的性能瓶颈. 为满足大数据处理对算力提升的需求, 需要研究集成芯片技术[107], 通过多芯粒集成的软硬件协同创新, 突破单芯片的规模、复杂度瓶颈, 实现大算力存算一体芯片, 为存算一体新范式的实现提供硬件基础. 在计算原理层面, 通过模拟存内计算, 实现对海量原始数据的事件驱动型处理, 提取有用信息, 实现稀疏性计算; 采用定制逻辑门的数字存内计算, 实现对数据的高精度处理, 并实现与GPU 等传统计算单元的标准数字化接口, 为存算芯片与GPU的异质系统建立基础. 此外, 多芯粒技术可以提高芯片的灵活性、可扩展性和可维护性, 同时也可以降低芯片制造的成本和风险. 此外, 在单个封装体内复用同一计算芯粒技术, 可以在不增加设计复杂度的基础上, 加快芯片设计和制造的速度, 同时也可以提高芯片的算力. 但是, 这需要解决芯粒间互连的难题, 为此, 通过专用的IO通信芯粒, 对外支持 PCIe等标准通信协议与接口, 对内实现存算一体间复杂的接口调度, 实现存算一体芯片与传统计算单元(如GPU等)的规模可扩展异构存算一体平台.

(3)大算力存算一体芯片的高效能量管理. 随着集成芯片系统规模的增长, 其所消耗的电流突破百安培量级, 而其工作电压持续降低至1 V甚至以下, 这些发展趋势为电源管理电路的设计提出了严峻的挑战[108]. 为满足大算力存算一体芯片的高效功率传输需求, 需要研究功率转换拓扑结构[109], 发展融合开关电感与电容结构的混合型架构, 有效提高电源管理电路在大负载电流与小输出电压条件下的转换效率; 在控制方法上, 研究优异的瞬态响应和输出电压调制性能, 满足集成芯片在计算时序等方面的严苛要求; 与此同时, 高功率高效电源管理技术对电感和电容等无源器件具有极高的要求, 因此, 需要从材料与磁学元器件等底层基础方面开展研究, 发展高性能无源器件及其集成技术, 实现全集成功率系统, 突破功率密度瓶颈, 实现紧凑型负载点电源管理系统. 在功率半导体技术上, 经过近50年的发展, 硅基功率器件性能已经接近其物理极限, 而基于氮化镓等宽禁带半导体在高压高功率领域展现出极大的优势, 但缺少互补型器件成为制约其发展高性能控制电路的瓶颈. 为此, 研究硅基/宽禁带化合物半导体的异质功率系统有望在功率处理性能与控制性能上取得优化设计.

3 超越摩尔时代半导体集成未来重点研究方向

随着全球科技迅猛发展, 数据处理需求的不断增长使传统集成电路架构暴露出性能瓶颈, 急需突破现有材料、器件和架构的限制, 提升计算效率并降低功耗. 如何应对这些挑战, 成为了科研和工程领域的关键任务. 为此, 全球领先的科技前沿研究机构和学者正在聚焦于新一代计算架构、光电异质融合集成、人工智能芯片、存算一体技术等领域, 推动多域多场异质集成技术的研究, 促进我国在集成电路领域取得突破性进展. 目前, 我国超越摩尔时代的集成新路径与新技术研究的重点方向与目标主要包括以下几方面.

(1)半导体材料的突破与高性能光电异质融合集成. 面对日益增长的数据处理需求, 新一代计算架构的研发显得尤为迫切. 突破现有材料的性能极限, 探索新一代半导体材料, 如二维材料、三维异质集成技术等, 将成为研究的重点. 同时, 光计算与光处理技术将成为未来计算架构的重要组成部分, 通过光互联与光接口技术, 实现高速、低功耗的数据传输与处理. 此外, 集成自旋量子比特和硅基光电融合集成技术研究, 也为量子计算和光电融合计算提供新的解决方案. 未来, 研究将集中在发展新一代光子计算架构及技术, 突破现有计算架构的速率和功耗瓶颈, 推动光电融合计算技术的应用. 同时, 掌握高速低功耗光互联与光接口技术, 着力推进光传–光算–电存的光电融合集成光子计算技术发展, 实现多材料体系光电融合集成芯片的片上规模持续增长, 推动光电融合计算技术的实际应用落地.

随着多领域、多场的跨界融合, 异质集成技术已成为集成电路研究的核心内容. 我国将加强新一代半导体材料、设计与制造的协同优化, 特别是在光电融合异质异构体系、功率/射频与Si基CMOS的异质集成路径上实现突破. 通过发展新的异质集成技术, 打破不同材料系统之间的兼容壁垒, 推动融合不同材料体系的光电子器件与微电子器件, 实现高性能、低功耗、小型化和智能化的计算系统. 在具体研究内容上, 重点发展高性能的光电子单元器件, 如窄线宽/多波长激光器、宽频带低功耗高线性电光调制器及阵列等. 同时, 充分挖掘和利用不同材料体系的优势, 如硅基、III-V族半导体、铌酸锂、钽酸锂、低维材料、宽禁带半导体等, 通过多材料体系的融合集成, 提升系统整体性能.

此外, Micro-LED在数据中心和高性能计算系统中的通信效率提升具有巨大潜力. 通过实现电信号到光信号的高效转换, Micro-LED可以提升芯片间通信效率, 特别是在数据中心和高性能计算系统中. 未来5年内, 需要突破大尺寸晶圆均匀性和红光缺失等材料问题, 发展Micro-LED在短距离高速数据传输中的传输能力. 同时, 着力推进Micro-LED与硅基CMOS驱动的光电互连芯片的研发与应用, 掌握高亮度、宽带宽Micro-LED芯片技术, 实现与VLC系统的集成以及低功耗、高速率光电互连方案在数据中心和AI大算力系统中的应用.

(2)超大规模存算一体架构与AI人工智能芯片. 高性能计算芯片在存力提升上面临瓶颈, 急需发展存算一体集成电路芯片技术以突破这一局限. 通过先进封装技术实现更高的存储密度、带宽和能效是解决这一问题的关键. 然而, 多器件多芯粒异质集成的兼容性问题、异构存算一体架构的设计与实现以及多工艺融合的存算一体芯片自动化设计理论等仍是当前面临的挑战. 对此, 需要开展深入研究新材料和新原理的存储技术, 解决硅基存储器速度、保持和大规模集成难以兼容的问题. 同时, 加强存算一体底层技术的研究, 如材料和界面的不理想特性对器件性能的影响规律、Si基CMOS兼容的高密度集成技术等. 未来, 发展面向存内计算的新型存储器件与芯粒集成技术, 掌握多工艺融合的存算一体芯片自动化设计理论, 着力推进芯粒集成大芯片的研制, 为高性能计算芯片的发展提供新的解决方案, 实现计算与存储融合的计算范式革新, 获得存算一体化领域的自主可控技术.

(3)宽禁带高功率器件与高速射频通信芯片. 功率半导体与射频器件是宽禁带半导体技术的重要组成部分, 对国家安全、产业安全和强国建设具有重大意义. 未来一个时期内, 将重点发展更高压、更低压、更高集成的宽禁带半导体电力电子器件以及高功率、更高频率的宽禁带半导体射频器件. 同时, 推进宽禁带半导体功率/射频器件与Si基CMOS的异质集成技术研究, 解决宽禁带半导体材料的生长与制备、器件设计与制造工艺等关键难题. 特别是在新能源汽车领域, 需要研发高可靠性、高压宽禁带半导体功率器件, 并实现与Si基CMOS的异质集成, 为电动汽车、AI算力中心和新能源发电领域提供高效、可靠的电力电子与射频器件解决方案.

4 超越摩尔时代的发展思考与建议

本文对超越摩尔时代半导体集成技术的现状与发展趋势、关键科学问题、未来重点研究方向等进行了分析, 并提出了超越摩尔时代半导体集成技术发展的思考和建议.

探索前沿基础研究方面, 聚焦于基础研究和科学问题的突破, 特别是在高性能、新功能、新机制及新应用导向下的新材料、新器件与新架构的融合创新, 超越传统框架探索新路径与解决方案, 支撑超越摩尔时代半导体领域的持续发展, 并为产业界提供技术支持与创新源泉. 着力提升原始创新能力, 探索前沿科学问题, 鼓励科研人员提出新理论、新方法与新技术, 为半导体领域注入新活力. 高度重视学科间交叉融合, 推动物理、化学、材料科学、电子工程等多学科深度融合与交叉创新, 共同攻克关键技术挑战, 通过联合研究项目和跨学科研究平台等方式, 促进学术交流与合作, 提升整体研究与创新水平.

产业应用基础研究方面, 当前急需加强设计工具研发, 特别是在异质集成系统分析设计方面, 以提升设计精度与效率; 同时, 要实现科学问题与工程问题的深度融合, 全面打通技术全链条, 确保产品质量. 企业应搭建平台, 推动协同创新, 特别是在异质异构集成研究上, 以提升全球竞争力. 此外, 还需打破壁垒, 实现应用与技术驱动的有机结合, 加强产业界、学术界与政府部门间的合作, 形成协同发展的良好生态.

系统牵引与重点方向系统布局, 深入研究“多域多场异质集成技术”, 推动新材料、新器件、新架构的融合创新以支撑半导体领域持续发展; 以应用为导向, 促进产研深度融合, 打破前沿与应用研究壁垒; 强化学科交叉与协同研究, 组建跨学科、跨校企团队, 针对超越摩尔时代半导体集成的共性关键技术进行联合攻关, 激发原始创新活力.

超越摩尔时代的发展需要持续的创新与协同努力. 通过聚焦前沿基础研究、加强产业应用基础研究、推动系统牵引与重点方向布局, 我们能够不断突破技术瓶颈, 推动半导体产业的持续进步. 未来, 我们期待产业界、学术界与政府部门的紧密合作, 共同探索超越摩尔时代半导体技术的新路径, 为全球半导体产业的发展贡献智慧与力量.

本文根据国家自然科学基金委员会第393期“双清论坛”讨论的内容整理。全文出版在《中国科学:信息科学》2025年55卷第6期上。